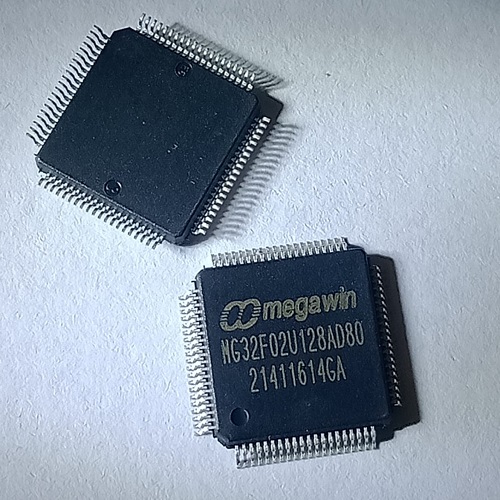

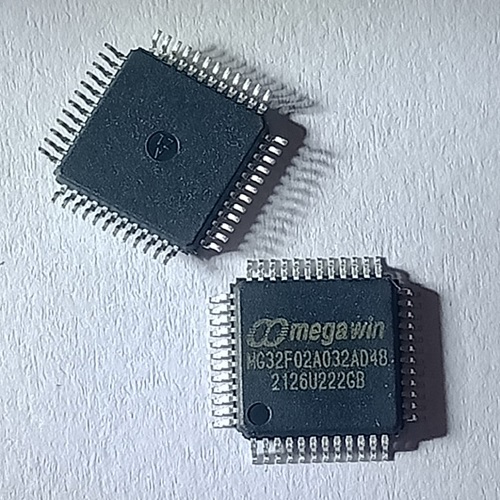

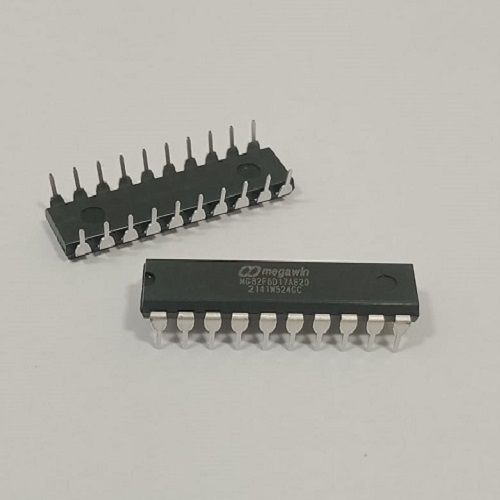

Megawin ARM Cortex M0 MCU MG32F02U128AD

9 in stock (can be backordered)

| ARM Cortex-M0 MCU

Flash ROM: 128 KB RAM: 16KB IO’s: 59/73 Timer: 7+RTC Communication: UART x7, I2C x2, SPI/QPI/OPI, USB, EMB, CRC, DMA LQFP-64/80 |

₹159.30

₹135 + 18% GST

Availability: 9 in stock (can be backordered)

9 in stock (can be backordered)

The MG32F02U128AD support multiple and flexible communicate interface for production application. It

provides alternate function pins those are including of GPIO, I2C, SPI, UART, Timer with IC/PWM, ADC,

Analog Comparator, DAC, EMB, NCO, CCL and SWD(on chip debug). It has maximum 73 GPIO pins and

provides programmable IO type – quasi-bidirectional , push-pull output , open-drain output , input only(Hi-z) with

optional pull-high. In addition, it is built-in internal de-bounce circuit to deglitch noise for worse signals.

- CPU Core

- ARM 32-bit Cortex-M0 CPU

- Operation frequency up to 48MHz

- Built-in one NVIC for 32 external interrupt inputs with 4-level priority

- Built-in one 24-bit system tick timer

- Built-in one single-cycle 32-bit multiplier

- Built-in one SWD serial wire debugger with 2 watch points and 4 breakpoints

- Flash Memory

- Built-in embedded max. 128K bytes flash memory for application code

- Support ICP (In-circuit program) for ISP boot code update through SWD interface

- Support ISP (In-system program) for application code update

- ▬ Support programmable ISP flash memory size for ISP boot code

- Support IAP (In-application program) for application data update

- ▬ Support programmable IAP flash memory size

- SRAM Memory

- Built-in embedded max. 16K bytes SRAM

- ▬ Support private 2K bytes for DMA and 14K bytes for software to improve access performance

- Built-in extra 512 bytes SRAM for USB endpoints’ packet buffer.

- Power

- Built-in two embedded regulators for core logic power and USB analog macro

- Built-in brown-out detectors

- ▬ BOD0 detect 1.4V

- ▬ BOD1 detect by selected level 4.2V/3.7V/2.4V/2.0V

- ▬ BOD2 detect 1.7V

- Built-in a power management controller with power-down and wakeup control

- Support three power operation modes

- ▬ ON(Normal) mode and SLEEP , STOP power down modes

- Support wake-up from SLEEP/STOP modes via multiple sources

- Reset

- Built-in embedded POR (power-on reset) circuit

- Built-in one reset source controller

- ▬ Programmable chip cold reset and warm reset for reset source

- ▬ Independent software reset control for internal modules

- Provide multiple reset source

- ▬ POR/BOD/External reset pin input/Software force reset

- ▬ IWDT/WWDT/ADC/Analog Comparator

- ▬ Illegal address error reset/Flash access protect error reset

- ▬ Missing clock detect (MCD) reset

- Clock

- Built-in embedded ILRCO (internal low frequency RC oscillator) by 32KHz

- Built-in embedded IHRCO (internal high frequency RC oscillator)

- ▬ Trimmed to 11.059 or 12MHz ±1% at +25℃

- Built-in embedded PLL clock output for system clock

- Built-in embedded XOSC oscillator with MCD for external 32KHz and 4 ~ 25MHz

- Support external clock input up to 36MHz

- Built-in a clock source controller with independent clock enable control for modules

- Support internal XOSC oscillator and internal ILRCO/IHRCO clock output

Leave a Reply